Servizos de fabricación electrónica integral, axúdanche a conseguir facilmente os teus produtos electrónicos a partir de PCB e PCBA

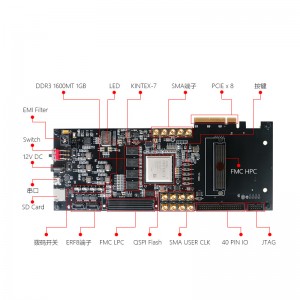

FPGA Xilinx K7 Kintex7 PCIe comunicación por fibra óptica

- DDR3 SDRAM: 16 GB de memoria DDR3 de 64 bits, velocidade de datos de 1600 Mbps

- Memoria flash QSPI: unha peza de memoria flash QSPIP de 128 Mbit que se pode usar para ficheiros de configuración de FPGA e almacenamento de datos de usuario.

- Interface PCLEX8: A interface PCLEX8 estándar úsase para comunicarse coa comunicación PCIE da placa base do ordenador. É compatible co estándar PCI Express 2.0. A velocidade de comunicación dun só canal pode chegar aos 5 Gbps.

- Porto serie USB UART: un porto serie, conéctase ao PC a través do cable miniUSB para realizar a comunicación serie

- Tarxeta Micro SD: asento para tarxetas MicroSD completamente, podes conectar a tarxeta MicroSD estándar

- Sensor de temperatura: un chip de sensor de temperatura LM75, que pode monitorizar a temperatura ambiental arredor da placa de desenvolvemento

- Porto de extensión FMC: un FMC HPC e un FMCLPC, que poden ser compatibles con varias tarxetas de expansión estándar

- Terminal de conexión de alta velocidade ERF8: 2 portos ERF8, que admiten transmisión de sinal de ultra alta velocidade. Extensión de 40 pines: reservada unha interface IO de extensión xeral con 2,54 mm e 40 pines, O efectivo ten 17 pares, admite 3,3 V.

- A conexión periférica do nivel e o nivel de 5 V poden conectar os periféricos periféricos de diferentes interfaces 1O de propósito xeral

- Terminal SMA; 13 cabezas SMA chapadas en ouro de alta calidade, o que é conveniente para que os usuarios cooperen con tarxetas de expansión AD/DA FMC de alta velocidade para a recollida e procesamento de sinais

- Xestión do reloxo: Fonte multirreloxo. Inclúe a fonte de reloxo diferencial do sistema de 200 MHz SIT9102

- Cristal diferencial oscilante: cristal de 50 MHz e chip de xestión de reloxo programable SI5338P: tamén equipado con

- EMCCLK de 66 MHz. Pode adaptarse con precisión a diferentes frecuencias de reloxo de uso

- Porto JTAG: porto JTAG estándar de 2,54 mm e 10 puntadas, para descarga e depuración de programas FPGA

- Chip de monitorización de tensión de subreinicio: unha peza do chip de monitorización de tensión ADM706R e o botón co botón proporciona un sinal de reinicio global para o sistema

- LED: 11 luces LED, indican a fonte de alimentación da placa base, sinal config_done, FMC

- Sinal indicador de enerxía e 4 LED de usuario

- Tecla e interruptor: 6 teclas e 4 interruptores son botóns de reinicio de FPGA,

- O botón do programa B e 4 teclas de usuario están compostos. 4 interruptores de dobre coitelo simple

Escribe aquí a túa mensaxe e envíanosla

Categorías de produtos

-

Teléfono

-

Correo electrónico

-

Whatsapp

-

Skype

-

Skype

-

Skype